Student Projects

VE/VM450

Effective Rewriting Strategy for Digital Circuit Optimization

Instructors: Prof. Weikang Qian, Prof. Chong han

Team Members: Yifan Cao, Xingyun Mao, Hanyu Wang, Yujie Chen, Zhiyu Chen

Project Video

Team Members

Team Members:

Yifan Cao, Xingyun Mao, Hanyu Wang, Yujie Chen, Zhiyu Chen

Instructors:

Prof. Weikang Qian, Prof. Chong han

Project Description

Problem

Concept Generation

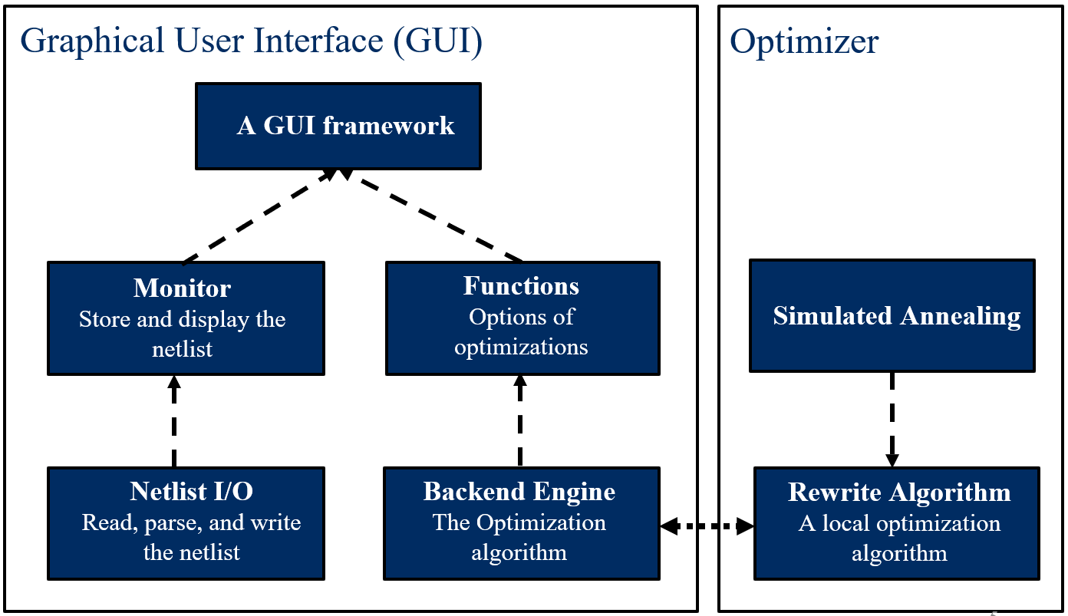

Design Description

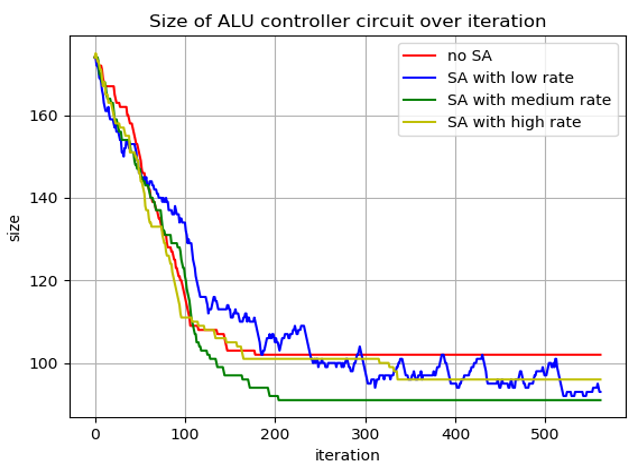

Implementation and Results

Validation

Validation Process:

For the effect of area reduction, compare the results of our program with that from original tool ABC. For run time, a timer in C++ can be used to measure it. For fraction of suitable circuits, we process a large amount sample circuits on our program and detect whether there are any bugs.

Some other specifications can also be verified using easy experiments.

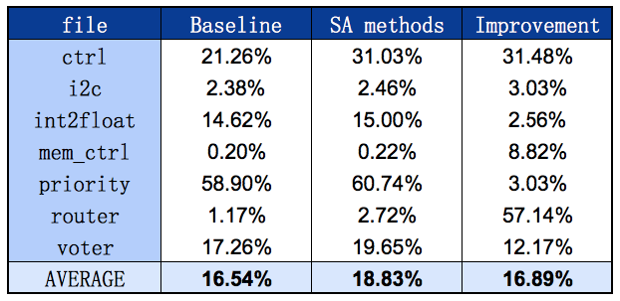

Validation Results:

According to validation part, most specifications can be met.

√ Fraction of circuit’s function not changed = 100 %

√ Fraction of area reduced >= 15%

√ Fraction of suitable circuits=100%

√ Runtime <= 600s

√ Number of command lines/clicks <=3

√ Correctness of visualized circuits

• Storage usage <= 30 MBytes

√ means verified and · means to be determined.