三支决赛队伍代表颁奖合照(左一为密院获奖队伍代表武馨悦同学)

该竞赛吸引了来自北京大学、华中科技大学、同济大学等高校的多支队伍参与。专项决赛论坛服务于CCF Chip 2024集成电路EDA算法加速挑战赛和定制计算算法实现挑战赛,赛题分为两个赛道,分别聚焦于AI4EDA与LLM消费级显卡的部署,旨在提升参赛学生在集成电路EDA、软硬件协同以及AI应用领域的创新和工程能力。该赛道的三支决赛获奖队伍全部为博士生。

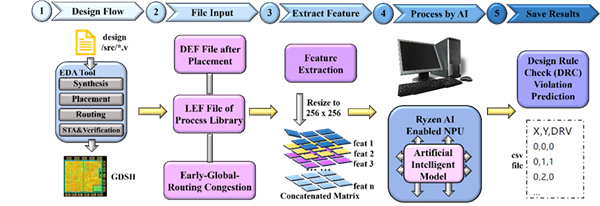

本次CCF-DAC挑战赛赛题旨在促进AI在ASIC EDA算法领域的应用,同时探索EDA算法在AI-PC平台的异构计算部署,进而提升EDA算法在AI-PC上的计算效率。

赛题流程

随着人工智能和大数据应用的不断发展,对于高性能、低功耗的ASIC(专用集成电路)芯片需求日益增长。然而,设计和验证ASIC芯片的过程中,面临着一个重要的挑战:设计规则检查(DRC)违例的预测和解决。DRC是芯片设计流程中的关键步骤之一,用于确保芯片布局和连线满足制造工艺的要求。DRC规则由芯片制造工艺厂商提供,通常包括关于金属线间距、晶体管尺寸等方面的规定。设计人员必须确保他们的设计不会违反这些规则,否则可能导致芯片生产失败或性能下降。

传统上,DRC是在设计完成后进行的,但随着芯片规模的不断增大和制造工艺的不断进步,DRC的复杂度也呈指数级增长。这导致了设计验证周期的延长和生产成本的增加。因此,提前识别可能的DRC违例并及时进行修复变得至关重要。AI在解决这一挑战中发挥了重要作用。通过利用大量历史设计数据和对应的DRC结果,可以训练AI模型来预测新设计中可能出现的DRC违例。这种方法可以大大加速设计验证过程,降低成本,并提高芯片的生产质量。

决赛答辩现场

队长武馨悦表示这次比赛让她深刻体会到集体的力量,“我觉得特别要感谢我们团队的每个人,在比赛中,我们彼此信任,相互支持,共同克服了一个又一个挑战。”同时这次比赛对她而言也起到了以赛促学,开拓眼界的作用,“通过这次难忘的经历,我们不仅学到了更多技术知识,也结交到了其他学校研究方向相似的同行伙伴,这让我们未来的成长发展受益匪浅。”

获奖学生简介

武馨悦

密西根学院2024级博士生

曾获“TI杯”上海市大学生电子设计竞赛二等奖等荣誉。目前主要研究方向为基于机器学习的电子设计自动化预测问题。

徐如歌

密西根学院2023级博士生

本科毕业于上海交通大学,硕士毕业于美国密西根大学信息学院。曾获密西根学院发展奖学金、优秀毕业生等荣誉。目前主要研究方向包括软硬件结合、边缘端AI和模型量化。

指导教师简介

郭鑫斐

上海交通大学密西根学院长聘教轨副教授

博士生导师,IEEE高级会员

博士毕业于弗吉尼亚大学计算机工程系,硕士毕业于佛罗里达大学电子与计算机工程系。曾任职于英伟达、IBM,作为主要贡献者参与了包括业界领先的第二代和第三代BlueField系列数据处理器DPU等多个芯片产品的研发工作,在集成电路设计、EDA和FPGA等领域会议期刊发表论文40余篇,出版著作1本,获得5次最佳论文、专题奖。目前担任期刊TVLSI副总主编、期刊Integration, the VLSI Journal的编委, 10多个领域内顶级会议的程序委员会成员, CCF开源发展委员会、容错专委执行委员等。主要研究兴趣包括低功耗高可靠性数字电路和系统、机器学习辅助EDA技术和可重构计算。