The University of Michigan – Shanghai Jiao Tong University Joint Institute (UM-SJTU JI, JI hereafter) Assistant Professor Xinfei Guo and his collaborators recently won the Best Paper Award at the 2022 IEEE 35th International System-on-Chip Conference (SOCC) for their work “RECO-HCON: A High-Throughput Reconfigurable Compact ASCON Processor for Trusted IoT”. This work is in collaboration with California Polytechnic State University and the University of Illinois Urbana-Champaign. JI undergraduate student Xiangdong Wei is the co-first author, Zhengping Zhu is the third author, and Xinfei Guo is the corresponding author.

Internet of Things (IoT) security has gained significant interests in recent years. Statistics show that in 2030 the number of connected IoT devices will reach 25.44 billion, which can lead to the security breach in the back-end of high-performance computing clusters connected with the same network. Unfortunately, the current security primitives are not suitable algorithms to be implemented on physically constrained devices designed for IoT. Thus, the National Institute of Standard and Technology of the United States has announced a worldwide lightweight cryptographic competition (LWC) for securing tiny devices.

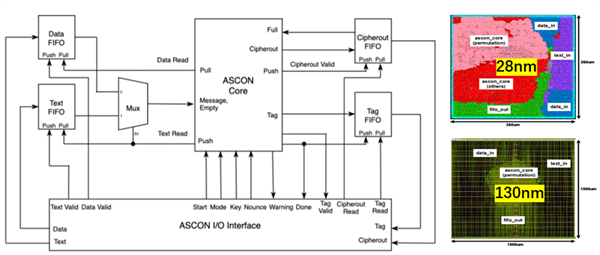

The proposed reconfigurable ASCON processor with full implementation in 28nm and 130nm technology nodes

This paper introduces a flexible, reconfigurable, and energy-efficient crypto-processor running one of the LWC finalist candidates – ASCON, which uses sponge construction that has fewer memory accesses that leads to less power consumption compared to other ones. The proposed processor is reconfigurable in a way both authenticated cipher (Encryption/decryption processes) and hash functions of ASCON are implemented in a six-mode compact fashion, covering a diversity of applications in the IoT spectrum. The design has been developed in Chisel and evaluated in 28/32nm technology with commercial EDA tools. Evaluation results show that the proposed processor achieves the highest throughput while consuming 29% less power, operating at over 667 MHz. The design has also been implemented in Skywater 130nm technology node with the latest released OpenLane design flow to ensure an end-to-end opensource delivery of the IP.

Certificate of Best Paper Award

Professor Mohamed EI-Hadedy from California Polytechnic State University receives the award on behalf of the team.

For 35 years the IEEE International System-on-Chip Conference (SOCC) has been the premier forum for sharing the latest advancements in SoC architecture, systems, logic and circuit design, process technology, test, design tools, and applications. This year it was held at the birthplace of the Titanic in Belfast, Northern Ireland. About 60 research papers were accepted and presented at the conference. The conference offers a three days technical program including keynote and plenary speeches, oral and poster presentations, hot-topic panel sessions, and two days industrial talks. Only one paper was selected to win the best paper award this year.

Personal Profile

Xiangdong Wei was a JI undergraduate student during 2018 – 2022, majoring in Electrical and Computer Engineering. He is now pursuing his Ph.D. degree at the University of Michigan.

Xinfei Guo is a tenure-track assistant professor at JI. He is a senior member of IEEE. He received his Ph.D. in Computer Engineering from the University of Virginia. He also holds a Master’s degree in Electrical and Computer Engineering from the University of Florida. Before joining JI, he worked at Nvidia and IBM research in US, where he served as a key member to contribute to multiple chip products, including the world-leading BlueField Data Processing Units (DPU) and a total of 7 chip tapeouts that cover a wide range of technology nodes from 180nm to 7nm. His previous work has results in over 40 conference or journal papers in IC design, EDA or FPGA fields. He also published a book. He serves as Associate Editor for Integration, the VLSI Journal, and PC member or chair positions for over 30 international conferences, such as DAC, CICC, ICCAD, ASPDAC, FCCM, HOST and so on. His current research interests include low power and high reliability computing, machine learning-assisted EDA techniques and reconfigurable computing.

Intelligent Circuits, Architectures, and Systems (iCAS) Lab

The iCAS lab aims at solving practical yet challenging research problems in the field of chip design. The research is at the intersections of circuits, architectures and systems. Our research mainly focuses on two thrusts, one is how to design a chip in an intelligent way; Second focus is on how to design an intelligent chip that is energy efficient and reliable. To achieve these goals, we look at the whole system stack and co-design methodologies, and we use AI and machine learning as a powerful tool to facilitate our research. We explore details to understand factors that set the chip design limit, investigate these unknowns with design practices, and develop optimal solutions to overcome these barriers. More details about the lab can refer to https://sites.ji.sjtu.edu.cn/icas.